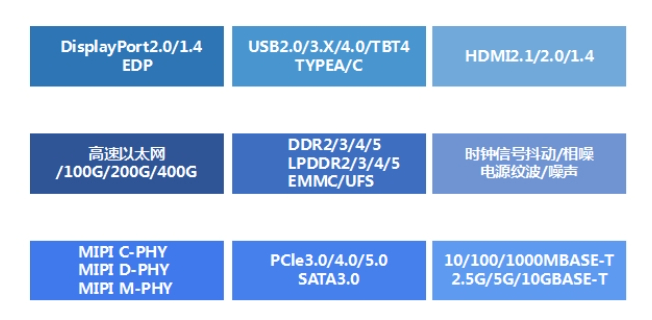

信息化UFS信號完整性測試回波損耗測試

UFS 信號完整性測試之接口設計要點

UFS 接口設計關乎信號完整性。接口處要保證良好的電氣連接,防止接觸不良導致信號中斷或失真。接口的阻抗要與傳輸線匹配,減少信號反射。在測試中,檢查接口的針腳布局是否合理,是否符合標準。例如,標準規定針腳布局要保證高速信號傳輸時信號質量穩定。優化接口設計,能為 UFS 信號完整性提供可靠連接,確保數據順暢傳輸。

UFS 信號完整性測試之電源穩定性影響

電源穩定性對 UFS 信號完整性至關重要。電源紋波過大,會引入噪聲,干擾信號傳輸。例如,要求電源紋波<50mVpp ,需配備大容量電容(10μF+0.1μF)濾波。若電源不穩定,信號可能出現抖動、失真等問題。在測試 UFS 信號完整性時,要同時監測電源質量。確保電源穩定,為 UFS 信號傳輸提供干凈、穩定的能源,保障信號完整性。 UFS 信號完整性測試之接口設計要點?信息化UFS信號完整性測試回波損耗測試

UFS 信號完整性測試之測試流程概述

UFS 信號完整性測試有嚴謹流程。首先搭建測試環境,連接好 UFS 設備、測試儀器等。接著對發射端進行測試,測量信號電壓、時間等參數。然后測試接收端,評估靈敏度與誤碼率。過程中,利用 TDR 測阻抗,用示波器觀察眼圖、抖動等。測試完成后,分析數據,判斷信號完整性是否達標。若不達標,排查問題并整改,重新測試,確保 UFS 信號滿足性能要求。

UFS 信號完整性測試之環境因素考量

測試 UFS 信號完整性時,環境因素不可忽視。溫度變化可能影響電子元件性能,導致信號參數改變。濕度太高,線路可能受潮,引發短路等問題,影響信號傳輸。電磁環境復雜,外界電磁干擾會使信號失真。所以,測試需在穩定溫濕度環境中進行,同時做好電磁屏蔽,減少環境因素對 UFS 信號完整性測試結果的干擾,保證測試準確性。 信號分析UFS信號完整性測試信號眼圖UFS 信號完整性測試之環境因素考量?

UFS 信號完整性重心要義

UFS 信號完整性,是確保 UFS 存儲設備內信號在傳輸路徑上保持完整的關鍵特性。在 UFS 系統里,數據借由各類信號進行存儲與傳輸,信號的完整性直接左右數據的準確性和系統穩定性。從本質上講,它聚焦于信號在傳輸過程中,能否維持原本的電壓、頻率、相位等關鍵參數。一旦信號完整性欠佳,數據傳輸便可能出錯,像數據丟失、誤碼等狀況就會接踵而至。比如在高速讀寫時,不穩定的信號或許會致使讀取到錯誤數據,寫入的數據也無法正確存儲。因此,保障 UFS 信號完整性,是實現 UFS 設備高效、可靠運行的基石,對提升存儲性能、確保數據安全起著決定性作用。

UFS 信號完整性測試之信號完整性與未來發展趨勢

UFS 信號完整性測試對 UFS 未來發展至關重要。未來,UFS 將向更高速率、更低功耗發展,信號完整性挑戰更大。通過持續優化測試方法,提前發現信號問題,能為 UFS 技術升級提供支持。例如,研發更先進測試設備,精細測量高速信號參數。重視信號完整性測試,是 UFS 順應未來發展趨勢,滿足市場對高性能存儲需求的必要條件。

UFS 信號完整性測試之信號完整性與產品創新

UFS 信號完整性測試助力產品創新。在研發新產品時,通過測試發現信號問題,促使工程師創新設計。如采用新線路布局、電路結構,解決信號完整性難題。良好的信號完整性為產品功能創新提供基礎,讓 UFS 設備實現更復雜應用。重視信號完整性測試,激發產品創新活力,推動 UFS 產品不斷升級。 UFS 信號完整性測試之自動化測試優勢?

UFS 信號完整性測試之信號完整性與抗振動性能

在車載、工業設備中,UFS 需具備抗振動能力,這與信號完整性相關。振動可能導致接口接觸不良、線路微形變,影響信號傳輸。測試時,通過振動臺模擬不同頻率、振幅的振動,監測信號參數變化。若振動中信號完整性明顯下降,需加固接口、優化線路固定方式。確保 UFS 在振動環境下信號穩定,是其在特殊領域應用的前提。

UFS 信號完整性測試之多通道同步測試要點

UFS 常采用多通道傳輸,多通道同步測試很重要。各通道信號需保持同步,否則會出現時序偏差,影響數據整合。測試時,用多通道示波器同時采集信號,分析通道間延遲。要求通道間延遲<0.1UI ,確保數據在接收端同步處理。若同步性差,需調整各通道線路長度、驅動能力,保證多通道信號協同傳輸,提升整體信號完整性。

UFS 信號完整性測試之接收端測試要點?物理層數字信號UFS信號完整性測試方案商

UFS 信號完整性測試之預編碼和調制技術作用?信息化UFS信號完整性測試回波損耗測試

UFS 信號完整性之電源完整性關聯

電源完整性與 UFS 信號完整性緊密相連。UFS 設備穩定工作依賴良好的電源供應。電源紋波過大,會在芯片內部產生噪聲,干擾信號傳輸,影響信號的電壓穩定性,導致信號電平波動,增加誤碼率。同時,電源分配網絡(PDN)的阻抗特性也至關重要。在高頻段,若 PDN 阻抗過高,會使電源電壓出現較大壓降,影響芯片正常工作,進而破壞信號完整性。例如,在設計 UFS 電源時,需使用大容量電容(如 10μF + 0.1μF)來降低電源紋波,構建低阻抗的 PDN,確保電源穩定,為 UFS 信號完整性創造良好的電源環境。 信息化UFS信號完整性測試回波損耗測試

- 重慶DDR4測試系列 2025-12-15

- 廣東眼圖測試PCIE3.0TX一致性測試信號完整性測試 2025-12-15

- 四川自動化DDR3測試 2025-12-15

- 自動化PCIE3.0TX一致性測試聯系人 2025-12-15

- 數字信號以太網1000M物理層測試HDMI測試 2025-12-15

- HDMI測試以太網1000M物理層測試多端口矩陣測試 2025-12-15

- 多端口矩陣測試DDR5測試聯系人 2025-12-15

- 信息化UFS信號完整性測試回波損耗測試 2025-12-15

- 測量PCIE3.0TX一致性測試執行標準 2025-12-15

- 甘肅DDR5測試協議測試方法 2025-12-15

- 深圳汽車載荷傳感器直銷價格 2025-12-15

- 生物醫藥用pH自動控制加液系統多少錢 2025-12-15

- 唐山HV顯微硬度計哪家好 2025-12-15

- 東宇膜分離制氮機對比 2025-12-15

- 四川梓盟門尼粘度儀價格咨詢 2025-12-15

- 耐酸堿襯氟止回閥定制 2025-12-15

- 迅杰光遠甲醇檢測儀器多少錢 2025-12-15

- 吉林易操作硬度計工廠直銷 2025-12-15

- 重慶智能型移液工作站代理 2025-12-15

- 鄭州準確度高石英石纖維直徑智能報告系統哪家技術強 2025-12-15