HTCC電子元器件鍍金貴金屬

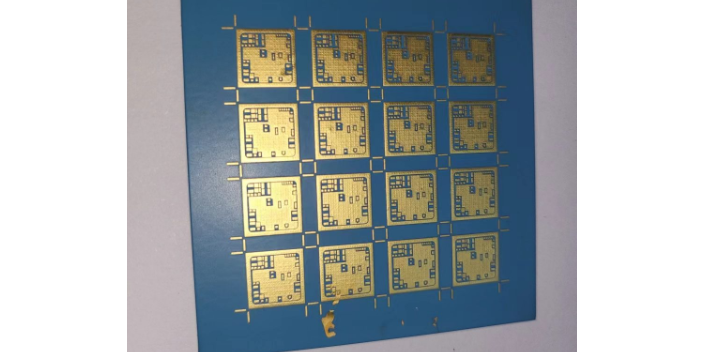

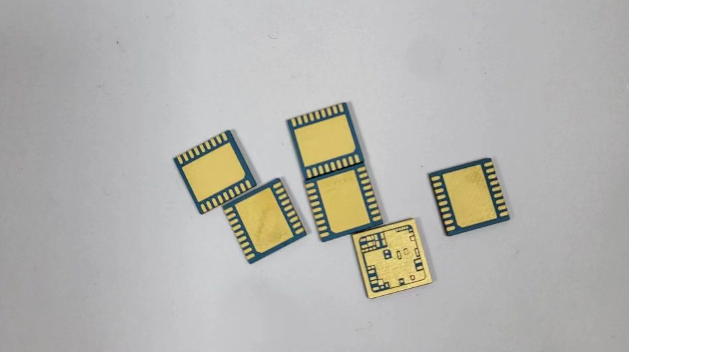

蓋板鍍金的工藝特性與應用場景蓋板鍍金作為精密制造領域的關鍵表面處理技術,通過電化學沉積或真空鍍膜工藝,在蓋板基材表面形成均勻、致密的金層。其重心優勢在于金材質的化學穩定性與優異導電性,使其廣泛應用于電子通信、航空航天、精密儀器等高級領域。例如,在半導體芯片封裝中,鍍金蓋板能有效保護內部電路免受外界環境腐蝕,同時降低信號傳輸損耗;在連接器組件中,鍍金層可減少插拔磨損,延長產品使用壽命,尤其適用于對可靠性要求極高的工業控制設備與醫療儀器。微型電子元件鍍金,在有限空間內實現高效導電。HTCC電子元器件鍍金貴金屬

陶瓷片的機械穩定性直接關系到其在安裝、使用及環境變化中的可靠性,而鍍金層厚度通過影響鍍層與基材的結合狀態、應力分布,對機械性能產生明顯調控作用,具體可從以下維度展開:

一、鍍層結合力:厚度影響界面穩定性陶瓷與金的熱膨脹系數差異較大(陶瓷約 1-8×10??/℃,金約 14.2×10??/℃),厚度是決定兩者結合力的關鍵。

二、抗環境沖擊能力:厚度適配場景強度在潮濕、腐蝕性環境中,厚度直接影響鍍層的抗破損能力。厚度低于 0.6 微米的鍍層,孔隙率較高(每平方厘米>5 個),環境中的水汽、鹽分易通過孔隙滲透至陶瓷表面,導致界面氧化,使鍍層的抗彎折性能下降 —— 在 180° 彎折測試中,0.5 微米鍍層的斷裂概率達 30%,而 1.0 微米鍍層斷裂概率為 5%。

三、耐磨損性能:厚度決定使用壽命在需要頻繁插拔或接觸的場景(如陶瓷連接器),鍍層厚度與耐磨損壽命呈正相關。厚度0.8 微米的鍍層,在插拔測試(5000 次,插拔力 5-10N)后,鍍層磨損量約為 0.3 微米,仍能維持基礎導電與機械結構;而厚度1.2 微米的鍍層,可承受 10000 次以上插拔,磨損后剩余厚度仍達 0.5 微米,滿足工業設備 “百萬次壽命” 的設計需求。 重慶5G電子元器件鍍金電鍍線電子元器件鍍金通過提升耐腐蝕性,讓元件在酸堿工況下正常工作,拓寬應用場景。

蓋板作為電子設備、精密儀器的“外層屏障”,其表面處理直接影響產品壽命與性能,而鍍金工藝憑借獨特優勢成為高級場景的推薦。相較于鍍鉻、鍍鋅,鍍金層不僅具備鏡面級光澤度,提升產品外觀質感,更關鍵的是擁有極強的抗腐蝕能力——在中性鹽霧測試中,鍍金蓋板耐蝕時長可達800小時以上,遠超普通鍍層的200小時標準,能有效抵御潮濕、化學氣體等惡劣環境侵蝕。從性能維度看,鍍金蓋板的導電性能優異,表面電阻可低至0.01Ω/□,尤其適用于需要兼顧防護與信號傳輸的場景,如通訊設備接口蓋板、醫療儀器操作面板等。其金層厚度通常根據使用需求控制在0.8-2微米:薄鍍層側重裝飾與基礎防護,厚鍍層則針對高耐磨、高導電需求,比如工業控制設備的按鍵蓋板,通過1.5微米以上鍍金層可實現百萬次按壓無明顯磨損。當前,蓋板鍍金多采用環保型無氰工藝,搭配超聲波清洗預處理,確保鍍層均勻度誤差小于5%,同時減少對環境的污染。隨著消費電子、新能源行業對產品可靠性要求提升,鍍金蓋板的市場需求正以每年18%的速度增長,成為高級制造領域的重要配套環節。

電子元器件鍍金層的常見失效模式及成因分析在電子元器件使用過程中,鍍金層失效會直接影響產品導電性能、可靠性與使用壽命。結合深圳市同遠表面處理有限公司多年行業經驗,可將鍍金層常見失效模式歸納為以下五類,同時解析背后重心成因,為預防失效提供參考:1. 鍍層氧化變色表現為鍍金層表面出現泛黃、發黑或白斑,尤其在潮濕、高溫環境中更易發生。成因主要有兩點:一是鍍金層厚度不足(如低于 0.1μm),無法完全隔絕基材與空氣接觸,基材金屬離子擴散至表層引發氧化;二是鍍后處理不當,殘留的鍍液雜質(如氯離子、硫離子)與金層發生化學反應,形成腐蝕性化合物。例如通訊連接器若出現此類失效,會導致接觸電阻從初始的 5mΩ 上升至 50mΩ 以上,影響信號傳輸。2. 鍍層脫落或起皮鍍層電子元器件鍍金能降低接觸電阻,確保電流傳輸穩定,適配高頻電路需求。

電子元器件鍍金的環保工藝與合規標準 隨著環保要求趨嚴,電子元器件鍍金需兼顧性能與綠色生產。傳統鍍金工藝中含有的氫化物、重金屬離子易造成環境污染,而同遠表面處理采用無氰鍍金體系,以環保絡合劑替代氫化物,實現鍍液無毒化;同時搭建廢水循環系統,對鍍金廢水進行分類處理,金離子回收率達95%以上,水資源重復利用率超80%,有效減少污染物排放。在合規性方面,公司嚴格遵循國際環保標準:產品符合 RoHS 2.0 指令(限制鉛、汞等 6 項有害物質)、EN1811(金屬鍍層鎳釋放量標準)及 EN12472(金屬鍍層耐腐蝕性測試標準);每批次產品均出具第三方檢測報告,確保鍍金層無有害物質殘留。此外,生產車間采用密閉式通風系統,避免粉塵、廢氣擴散,打造綠色生產環境,既滿足客戶對環保產品的需求,也踐行企業可持續發展理念。航空航天領域中,電子元器件鍍金可抵抗極端溫差與輻射,確保航天器電路持續通暢。北京芯片電子元器件鍍金外協

芯片引腳鍍金,優化電流傳導,提升芯片運行效率。HTCC電子元器件鍍金貴金屬

電子元器件鍍金層厚度不足的重心成因解析 在電子元器件鍍金工藝中,鍍層厚度不足是影響產品性能的常見問題,可能導致導電穩定性下降、耐腐蝕性減弱等隱患。結合深圳市同遠表面處理有限公司多年工藝管控經驗,可將厚度不足的原因歸納為四大關鍵環節,為工藝優化提供方向: 1. 工藝參數設定偏差 電鍍過程中電流密度、鍍液溫度、電鍍時間是決定厚度的重心參數。若電流密度低于工藝標準,會降低離子活性,減緩結晶速度;而電鍍時間未達到預設時長,直接導致沉積量不足。2. 鍍液體系異常鍍液濃度、pH 值及純度會直接影響厚度穩定性。當金鹽濃度低于標準值(如從 8g/L 降至 5g/L),離子供給不足會導致沉積量減少;pH 值偏離比較好范圍(如酸性鍍金液 pH 從 4.0 升至 5.5)會破壞離子平衡,降低沉積效率;若鍍液中混入雜質離子(如銅、鐵離子),會與金離子競爭沉積,分流電流導致金層厚度不足。3. 前處理工藝缺陷元器件基材表面的油污、氧化層未徹底清理,會形成 “阻隔層”,導致鍍金層局部沉積困難,出現 “薄區”。4. 設備運行故障電鍍設備的穩定性直接影響厚度控制。HTCC電子元器件鍍金貴金屬

- 廣東陶瓷金屬化電子元器件鍍金供應商 2025-12-15

- 武漢精密五金表面處理廠 2025-12-15

- 河源真空陶瓷金屬化規格 2025-12-14

- 佛山金屬五金表面處理方法 2025-12-14

- 江蘇貼片電子元器件鍍金 2025-12-14

- 上海片式電子元器件鍍金鎳 2025-12-14

- 無錫金屬五金表面處理拋光加工 2025-12-14

- 揭陽金屬五金表面處理廠 2025-12-14

- 陜西新能源電子元器件鍍金銠 2025-12-14

- HTCC電子元器件鍍金貴金屬 2025-12-14

- 湖南地質勘探專業儀器線束定制化生產 2025-12-15

- 徐匯區貿易電子元器件怎么樣 2025-12-15

- 青海國產開關電源廠家電話 2025-12-15

- 無錫PCBsorting第三方 2025-12-15

- 東莞空氣能熱泵物聯網無線通訊哪個牌子好 2025-12-15

- 普陀區高密度腦電設備廠商 2025-12-15

- 中國澳門638nm激光器IntegratedOptics哪家好 2025-12-15

- 黃浦區質量電阻芯片銷售廠 2025-12-15

- 山西自動化電子測量儀器 2025-12-15

- 建鄴區不銹鋼無縫管推薦廠家 2025-12-15