數字信號UFS信號完整性測試物理層測試

UFS 信號完整性之信號上升 / 下降時間優化

優化信號上升 / 下降時間對 UFS 信號完整性意義重大。在 UFS 數據傳輸中,合適的上升 / 下降時間能減少信號間干擾,保障信號質量。若上升 / 下降時間過短,信號的高頻分量增加,會導致傳輸線損耗增大、串擾加劇;若過長,則信號傳輸速度受限,影響系統性能。例如,在設計 UFS 信號時,需根據傳輸線特性、系統頻率等因素,合理調整驅動芯片參數,優化信號的上升 / 下降時間。通過精確控制信號的變化速率,可使信號在保證傳輸速度的同時,降低信號完整性風險,實現高效、可靠的數據傳輸。 UFS 信號完整性測試之信號完整性與產品質量?數字信號UFS信號完整性測試物理層測試

UFS 信號完整性測試之自動化測試優勢

自動化測試在 UFS 信號完整性測試中優勢明顯。傳統手動測試效率低、易出錯,尤其在批量測試時。自動化測試通過編程控制儀器,可快速完成參數測量、數據記錄與分析。能在短時間內測試大量樣本,保證測試一致性。還可自動生成測試報告,便于追溯問題。采用自動化測試,能大幅提升 UFS 信號完整性測試效率與準確性,降低人工成本。

UFS 信號完整性測試之不同應用場景測試差異

UFS 在手機、汽車電子等不同場景應用,信號完整性測試有差異。手機對功耗敏感,測試需兼顧低功耗下的信號質量;汽車電子要求在 -40℃~125℃ 寬溫環境穩定,測試要模擬極端溫度。不同場景的電磁環境也不同,測試時電磁屏蔽措施需調整。針對場景特點設計測試方案,才能確保 UFS 在各領域都能可靠工作。 物理層數字信號UFS信號完整性測試方案UFS 信號完整性與傳輸線損耗?

UFS 信號完整性測試之接口設計要點

UFS 接口設計關乎信號完整性。接口處要保證良好的電氣連接,防止接觸不良導致信號中斷或失真。接口的阻抗要與傳輸線匹配,減少信號反射。在測試中,檢查接口的針腳布局是否合理,是否符合標準。例如,標準規定針腳布局要保證高速信號傳輸時信號質量穩定。優化接口設計,能為 UFS 信號完整性提供可靠連接,確保數據順暢傳輸。

UFS 信號完整性測試之電源穩定性影響

電源穩定性對 UFS 信號完整性至關重要。電源紋波過大,會引入噪聲,干擾信號傳輸。例如,要求電源紋波<50mVpp ,需配備大容量電容(10μF+0.1μF)濾波。若電源不穩定,信號可能出現抖動、失真等問題。在測試 UFS 信號完整性時,要同時監測電源質量。確保電源穩定,為 UFS 信號傳輸提供干凈、穩定的能源,保障信號完整性。

UFS 信號完整性測試之信號完整性與電磁兼容性

UFS 信號完整性與電磁兼容性緊密相關。良好的信號完整性可減少設備自身電磁輻射,降低對其他設備干擾。同時,設備能更好抵抗外界電磁干擾,保證信號傳輸不受影響。在測試中,既要檢查 UFS 信號完整性,也要評估其電磁兼容性。通過優化電路設計、采取屏蔽措施等,兼顧信號完整性與電磁兼容性,讓 UFS 設備在復雜電磁環境中正常工作。

UFS 信號完整性測試之信號完整性與系統兼容性

UFS 信號完整性影響系統兼容性。當 UFS 設備信號穩定,與其他系統組件能更好協同工作。若信號存在問題,可能與主板、處理器等不兼容,導致系統故障。在測試 UFS 信號完整性時,將其接入不同系統環境,測試兼容性。確保信號完整性,可提高 UFS 設備通用性,使其能在多種系統中穩定運行,擴大應用范圍。

UFS 信號完整性測試之信號完整性與抗振動性能?

UFS 信號完整性測試之維修中的信號檢測

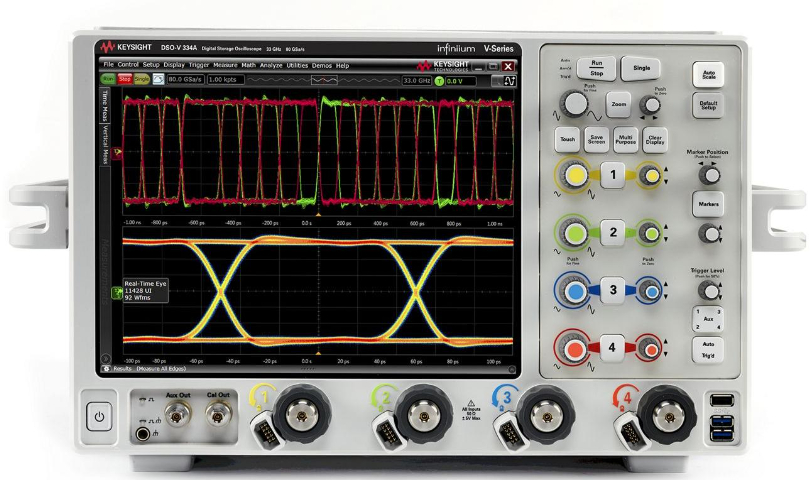

設備維修時,UFS 信號完整性檢測可快速定位故障。若設備頻繁死機,可檢測 UFS 信號是否存在反射、串擾。用簡易示波器測量信號波形,與正常波形比對。若信號失真嚴重,可能是接口氧化、線路損壞等。通過信號檢測,能縮小故障范圍,提高維修效率,減少盲目更換元件的成本,讓設備盡快恢復正常運行。

UFS 信號完整性測試之芯片級測試與板級測試區別

UFS 芯片級測試與板級測試有明顯區別。芯片級測試在芯片出廠前進行,關注芯片內部信號傳輸,需高精度探針臺配合。板級測試針對 PCB 板上的 UFS 模塊,側重線路、接口對信號的影響。芯片級測試確保芯片本身性能,板級測試評估系統集成后的信號質量。二者相輔相成,共同保障 UFS 從芯片到整機的信號完整性。 UFS 信號完整性測試之信號失真排查?高速接口UFS信號完整性測試檢測報告

UFS 信號完整性重心要義?數字信號UFS信號完整性測試物理層測試

電源完整性關聯VCCQ電源噪聲>50mV會導致眼高下降30%。建議布置10μF+0.1μF去耦組合,PDN阻抗<10mΩ@100MHz。實測數據:優化前后電源噪聲從85mV降至35mV。6.協議層影響UniPro鏈路訓練時需監測信號穩定性,L1→L4切換時間應<100μs。協議分析儀捕獲到CRC錯誤率>1E-12時,往往伴隨信號幅度下降5-10%。7.生產測試方案自動化測試系統應包含:眼圖掃描(20個參數)、抖動頻譜分析、電源紋波檢測。某產線50片測試數據顯示:合格率98.4%,主要失效模式為眼高不足(占比85%)。8.仿真對比實踐HyperLynx仿真與實測對比:插入損耗偏差應<0.5dB@5.8GHz。某設計仿真-2.1dB,實測-2.4dB,經優化過孔結構后一致率達99%。9.材料選擇影響不同PCB板材測試結果:Megtron6比FR4損耗降低40%@6GHz。高速層建議使用Dk=3.3±0.05的材料,玻纖效應導致阻抗波動需<±3Ω。10.ESD防護設計TVS二極管結電容>0.5pF會導致信號邊沿退化。實測數據:使用0.3pF器件后,上升時間從28ps改善至25ps,眼圖寬度增加0.05UI。數字信號UFS信號完整性測試物理層測試

- 轉接板UFS信號完整性測試插入損耗測試 2025-12-14

- 信號分析UFS信號完整性測試測試流程 2025-12-14

- 通信PCIE3.0TX一致性測試調試 2025-12-14

- 數字信號以太網1000M物理層測試多端口矩陣測試 2025-12-14

- 軟件測試UFS信號完整性測試方案商 2025-12-14

- 山西DDR4測試芯片測試 2025-12-14

- 廣東HDMI測試DDR5測試 2025-12-14

- 測試服務以太網1000M物理層測試TX/RX 2025-12-14

- 內蒙古DDR4測試推薦貨源 2025-12-14

- 數字信號UFS信號完整性測試物理層測試 2025-12-14

- 秦淮區品牌火星熄滅消音器 2025-12-14

- 湖南氯氣濃度在線監測儀 2025-12-14

- 溫州先導式電磁閥生產廠家 2025-12-14

- 鹽城徠卡顯微鏡檢測 2025-12-14

- 北京在線粒子檢測多少錢 2025-12-14

- 常州載荷傳感器直銷價格 2025-12-14

- 紹興電流傳感器 2025-12-14

- 湖北高精度pH自動控制加液系統 2025-12-14

- 云南采購消磁系統 2025-12-14

- 南通進口廢氣處理設備廠家直銷 2025-12-14