軟件測試UFS信號完整性測試端口測試

UFS 信號傳輸模式與完整性關系

UFS 有多種信號傳輸模式,像 Gear1 至 Gear4 。不同模式對應不同數(shù)據速率,如 Gear4 模式可達 11.6Gbps 。隨著速率提升,對信號完整性要求更高。高速傳輸時,信號易受干擾、發(fā)生失真。差分信號技術是 UFS 保障信號完整性的手段,發(fā)送兩個相位差 180 度信號,接收端通過比較消除共模干擾,讓信號在高速傳輸模式下,也能保持較高完整性,確保數(shù)據準確傳輸。

UFS 信號完整性測試之發(fā)射端測試要點

UFS 發(fā)射端測試是信號完整性測試重要部分。需測試發(fā)射端信號電壓電平、時間參數(shù)、信號質量等。信號電壓電平要符合規(guī)范,否則接收端無法正確識別信號。時間參數(shù)包括上升時間、下降時間等,影響信號傳輸速率與準確性。質量信號質量可減少誤碼。測試時用高頻示波器觀察信號,必要時加端接適配器,保證共模電平穩(wěn)定,確保發(fā)射端信號滿足 UFS 信號完整性標準。 UFS 信號完整性測試之信號完整性與行業(yè)標準遵循?軟件測試UFS信號完整性測試端口測試

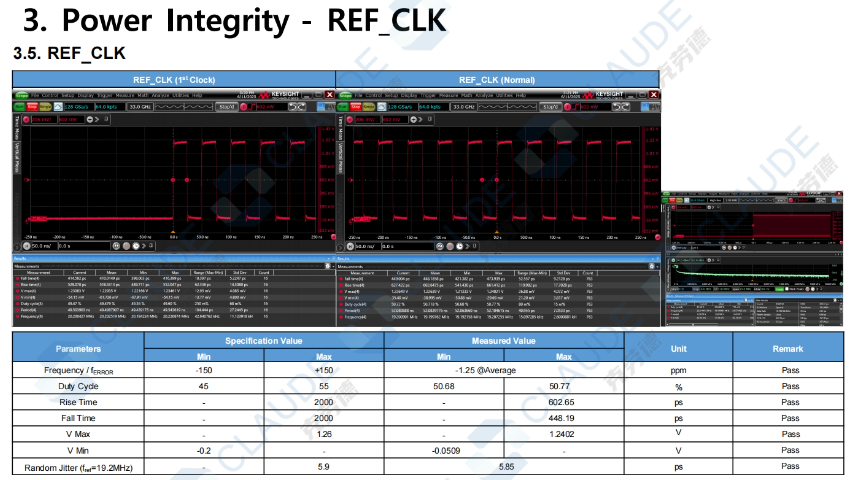

UFS 信號完整性之眼圖參數(shù)測試

眼圖參數(shù)是 UFS 信號完整性測試的關鍵指標。在 UFS 3.1 @11.6Gbps 速率下,要求眼高≥100mV,眼寬≥0.7UI 。眼高反映信號的噪聲容限,眼寬體現(xiàn)信號的時間裕量。當眼高不足,信號易受噪聲干擾;眼寬過窄,數(shù)據傳輸易出錯。通過專業(yè)設備測量眼圖參數(shù),能直觀評估信號質量。若參數(shù)不達標,需排查線路、接口等問題,優(yōu)化信號傳輸路徑,以滿足 UFS 信號完整性對眼圖參數(shù)的要求。

UFS 信號完整性之抖動測試抖動測試

在 UFS 信號完整性測試里不可或缺。總抖動(TJ)需<0.3UI,隨機抖動(RJ)<0.1UI 。抖動會使信號邊沿發(fā)生偏移,導致接收端誤判數(shù)據。TJ 包含 RJ 和確定性抖動,RJ 源于熱噪聲等隨機因素。測試抖動時,利用高精度儀器捕捉信號變化。若抖動超標,可從優(yōu)化電路布局、減少電磁干擾等方面著手。降低抖動,能有效提升 UFS 信號傳輸?shù)臏蚀_性與穩(wěn)定性。 測試原理UFS信號完整性測試高速信號傳輸UFS 信號完整性測試之信號完整性與抗振動性能?

UFS 信號完整性測試之信號完整性與用戶體驗

UFS 信號完整性直接影響用戶體驗。信號穩(wěn)定,設備讀寫速度快、運行流暢。當信號出現(xiàn)問題,手機等設備可能卡頓、文件傳輸失敗。在測試 UFS 信號完整性時,從用戶角度出發(fā),模擬實際使用場景。保障信號完整性,提升設備性能,為用戶帶來便捷、高效使用體驗,提高用戶滿意度。

UFS 信號完整性測試之常見誤區(qū)

UFS 信號完整性測試易陷入一些誤區(qū)。比如,*關注眼圖參數(shù)達標,忽視實際使用場景下的信號表現(xiàn)。有些測試在理想環(huán)境完成,未模擬設備振動、溫度驟變等情況,導致測試結果與實際脫節(jié)。還有人認為高成本測試設備就一定能保證測試精細,卻忽略操作規(guī)范。避免這些誤區(qū),需結合實際應用場景,規(guī)范操作流程,***評估信號完整性,才能讓測試真正發(fā)揮作用。

UFS 信號完整性測試之綠色環(huán)保設計考量

在綠色環(huán)保理念下,UFS 信號完整性測試需考慮相關設計因素。采用環(huán)保材料制作 PCB 板時,材料特性可能影響信號傳輸。例如,某些新型環(huán)保絕緣材料介電常數(shù)與傳統(tǒng)材料不同,可能導致信號延遲、損耗變化。測試時,要對比不同環(huán)保材料下 UFS 信號完整性表現(xiàn)。同時,優(yōu)化線路設計,減少能源消耗,降低信號傳輸過程中的功耗。在滿足信號完整性要求的基礎上,實現(xiàn) UFS 設備的綠色環(huán)保設計,既符合可持續(xù)發(fā)展趨勢,又保障設備性能。 UFS 硬件架構與信號完整性關聯(lián)?

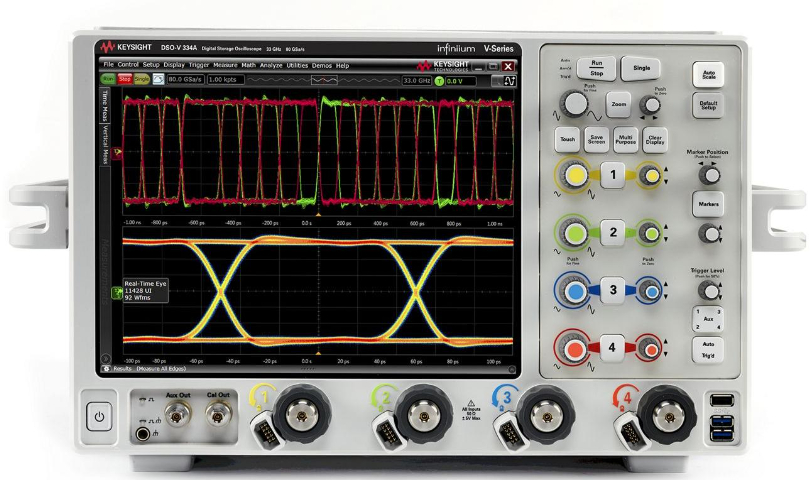

1.測試基礎要求UFS信號測試需在23±3℃環(huán)境進行,要求示波器帶寬≥16GHz(UFS3.1需33GHz),采樣率≥80GS/s。測試點應選在UFS芯片ballout1mm范圍內,使用40GHz差分探頭,阻抗匹配100Ω±5%。需同時監(jiān)測VCCQ(1.2V)和VCC(3.3V)電源噪聲。2.眼圖標準解讀JEDEC標準規(guī)定:HS-Gear3眼高≥80mV,眼寬≥0.7UI;HS-Gear4要求提升15%。實測需累積1E6比特數(shù)據,重點關注垂直閉合(噪聲導致)和水平閉合(抖動導致)。合格樣本眼圖應呈現(xiàn)清晰鉆石型。3.抖動分解方法使用相位噪聲分析軟件將總抖動(Tj)分解:隨機抖動(Rj)應<1.5psRMS,確定性抖動(Dj)<5psp-p。某案例顯示時鐘樹布局不良導致14ps周期性抖動,通過優(yōu)化走線降低至6ps。4.阻抗測試要點TDR測試顯示UFS走線阻抗需控制在100Ω±10%,BGA區(qū)域允許±15%。某6層板測試發(fā)現(xiàn):線寬4mil時阻抗波動達20Ω,改為3.5mil+優(yōu)化參考層后穩(wěn)定在102±3Ω。UFS 信號完整性測試之故障模擬測試方法?自動化UFS信號完整性測試阻抗測試/TDR測試/回波損耗測試

UFS 信號完整性測試之新興測試技術應用?軟件測試UFS信號完整性測試端口測試

UFS 信號完整性測試之不同版本 UFS 測試差異

不同版本 UFS 信號完整性測試有差異。UFS 4.0 比 UFS 3.1 傳輸速率更高,測試時對儀器帶寬、采樣率要求更嚴。UFS 4.0 需測試 23.2Gbps 速率下的信號,而 UFS 3.1 比較高 11.6Gbps 。高版本 UFS 對眼圖參數(shù)、抖動控制更苛刻。測試時需根據具體版本調整測試標準與儀器設置,確保測試符合對應版本的技術規(guī)范。

UFS 信號完整性測試之供應鏈測試協(xié)作

UFS 供應鏈中,各環(huán)節(jié)測試協(xié)作很重要。芯片廠商、板卡制造商、整機廠商需統(tǒng)一測試標準。芯片廠商提供芯片信號參數(shù),板卡廠商測試板級信號完整性,整機廠商進行系統(tǒng)級測試。通過共享測試數(shù)據,及時發(fā)現(xiàn)設計、生產環(huán)節(jié)的信號問題。良好的協(xié)作能縮短產品研發(fā)周期,降低成本,確保蕞終產品 UFS 信號完整性達標。 軟件測試UFS信號完整性測試端口測試

- 北京DDR4測試銷售價格 2025-12-13

- 信息化UFS信號完整性測試操作 2025-12-13

- 軟件測試UFS信號完整性測試保證質量 2025-12-13

- 數(shù)字接口測試系列UFS信號完整性測試示波器和探頭治具 2025-12-13

- 數(shù)字信號LVDS發(fā)射端一致性測試推薦貨源 2025-12-13

- 多端口矩陣測試DDR3測試一致性測試 2025-12-13

- PCI-E測試LVDS發(fā)射端一致性測試推薦貨源 2025-12-13

- 夾具測試UFS信號完整性測試測試流程 2025-12-13

- 軟件測試UFS信號完整性測試端口測試 2025-12-13

- 遼寧測試服務DDR3測試 2025-12-13

- 是德模塊化任意波形發(fā)生器M8195A采購 2025-12-13

- 海安本地光學膜供應商 2025-12-13

- 專業(yè)液體閃爍譜儀價格優(yōu)惠 2025-12-13

- 徐匯區(qū)轉軸扭力測試儀 2025-12-13

- 青浦區(qū)本地機械設備銷售調試 2025-12-13

- 四川FLASH熱流儀生產廠家 2025-12-13

- 鹽城內置式磁致伸縮傳感器定做 2025-12-13

- 湖南視頻光學接觸角測量儀產品介紹 2025-12-13

- 上海JS94微電泳儀哪家好 2025-12-13

- 連云港EYELA旋蒸套裝 2025-12-13