中山金屬刻蝕材料刻蝕加工平臺

電容耦合等離子體刻蝕(CCP)是通過匹配器和隔直電容把射頻電壓加到兩塊平行平板電極上進行放電而生成的,兩個電極和等離子體構成一個等效電容器。這種放電是靠歐姆加熱和鞘層加熱機制來維持的。由于射頻電壓的引入,將在兩電極附近形成一個電容性鞘層,而且鞘層的邊界是快速振蕩的。當電子運動到鞘層邊界時,將被這種快速移動的鞘層反射而獲得能量。電容耦合等離子體刻蝕常用于刻蝕電介質等化學鍵能較大的材料,刻蝕速率較慢。電感耦合等離子體刻蝕(ICP)的原理,是交流電流通過線圈產生誘導磁場,誘導磁場產生誘導電場,反應腔中的電子在誘導電場中加速產生等離子體。通過這種方式產生的離子化率高,但是離子團均一性差,常用于刻蝕硅,金屬等化學鍵能較小的材料。電感耦合等離子體刻蝕設備可以做到電場在水平和垂直方向上的控制,可以做到真正意義上的De-couple,控制plasma密度以及轟擊能量。隨著生物醫學領域對硅的不斷提高,深硅刻蝕設備也需要不斷地進行創新和改進。中山金屬刻蝕材料刻蝕加工平臺

等離子體表面處理技術是一種利用高能等離子體對物體表面進行改性的技術,它可以實現以下幾個目的:清洗:通過使用氧氣、氮氣、氬氣等工作氣體,將物體表面的有機物、氧化物、粉塵等污染物去除,提高表面的潔凈度和活性;刻蝕:通過使用氟化氫、氯化氫、硫化氫等刻蝕氣體,將物體表面的金屬、半導體、絕緣體等材料刻蝕掉,形成所需的圖案和結構;沉積:通過使用甲烷、硅烷、乙炔等沉積氣體,將物體表面的碳、硅、金屬等材料沉積上,形成保護層或功能層;通過使用空氣、水蒸氣、一氧化碳等活性氣體,將物體表面的極性基團增加或改變,提高表面的親水性或親福建感應耦合等離子刻蝕材料刻蝕平臺電容耦合等離子體刻蝕常用于刻蝕電介質等化學鍵能較大的材料。

硅材料刻蝕技術的演進見證了半導體工業的發展歷程。從早期的濕法刻蝕到現在的干法刻蝕,每一次技術的革新都推動了半導體技術的進步。濕法刻蝕雖然工藝簡單,但難以滿足高精度和高均勻性的要求。隨著ICP刻蝕等干法刻蝕技術的出現,硅材料刻蝕的精度和效率得到了卓著提升。然而,隨著集成電路特征尺寸的不斷縮小,對硅材料刻蝕技術的要求也越來越高。未來,硅材料刻蝕技術將向著更高精度、更低損傷和更環保的方向發展。科研人員將不斷探索新的刻蝕機制和工藝參數,以進一步提高刻蝕精度和效率,降低生產成本,為半導體工業的持續發展提供有力支持。

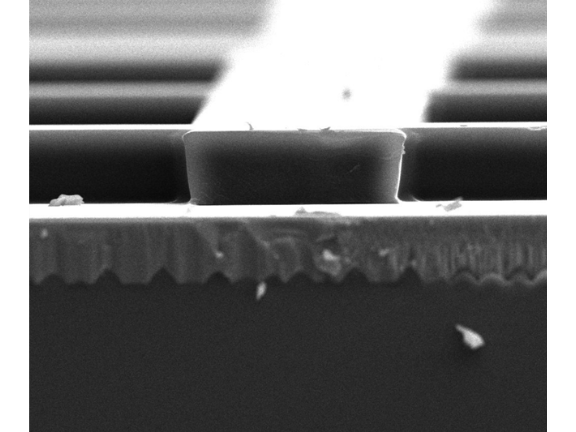

深硅刻蝕設備在半導體領域有著重要的應用,主要用于制造先進存儲器、邏輯器件、射頻器件、功率器件等。其中,先進存儲器是指采用三維堆疊或垂直通道等技術實現高密度、高速度、低功耗的存儲器,如三維閃存(3DNAND)、三維交叉點存儲器(3DXPoint)、磁阻隨機存取存儲器(MRAM)等。深硅刻蝕設備在這些存儲器中主要用于形成垂直通道、孔陣列、選擇柵極等結構。邏輯器件是指用于實現邏輯運算功能的器件,如場效應晶體管(FET)、互補金屬氧化物半導體(CMOS)等。深硅刻蝕設備在這些器件中主要用于形成柵極、源漏區域、隔離區域等結構。深硅刻蝕設備的缺點包含扇形效應,荷載效應,表面粗糙度,環境影響,成本壓力等。

氧化鎵刻蝕制程是一種在半導體制造中用于形成氧化鎵(Ga2O3)結構的技術,它具有以下幾個特點:?氧化鎵是一種具有高帶隙(4.8eV)、高擊穿電場(8MV/cm)、高熱導率(25W/mK)等優異物理性能的材料,適合用于制作高功率、高頻率、高溫、高效率的電子器件;氧化鎵可以通過水熱法、分子束外延法、金屬有機化學氣相沉積法等方法在不同的襯底上生長,形成單晶或多晶薄膜;氧化鎵的刻蝕制程主要采用干法刻蝕,即利用等離子體或離子束對氧化鎵進行物理轟擊或化學反應,將氧化鎵去除,形成所需的圖案;氧化鎵的刻蝕制程需要考慮以下幾個因素:刻蝕速率、選擇性、均勻性、側壁傾斜度、表面粗糙度、缺陷密度等,以保證刻蝕的質量和精度。深硅刻蝕設備的控制策略是指用于實現深硅刻蝕設備各個部分的協調運行和優化性能的方法。IBE材料刻蝕

等離子體表面處理技術是一種利用高能等離子體對物體表面進行改性的技術。中山金屬刻蝕材料刻蝕加工平臺

感應耦合等離子刻蝕(ICP)技術是一種先進的材料加工手段,普遍應用于半導體制造、微納加工等領域。該技術利用高頻電磁場激發產生高密度等離子體,通過物理轟擊和化學反應雙重作用,實現對材料的精確刻蝕。ICP刻蝕具有高精度、高均勻性和高選擇比等優點,特別適用于復雜三維結構的加工。在微電子器件的制造中,ICP刻蝕技術能夠精確控制溝道深度、寬度和側壁角度,是實現高性能、高集成度器件的關鍵工藝之一。此外,ICP刻蝕還在生物芯片、MEMS傳感器等領域展現出巨大潛力,為微納技術的發展提供了有力支持。中山金屬刻蝕材料刻蝕加工平臺

- 山東NEMS器件電子束曝光服務 2025-12-16

- 安徽光芯片電子束曝光工藝 2025-12-16

- 四川精密加工電子束曝光價錢 2025-12-16

- 河北圖形化電子束曝光工藝 2025-12-16

- 四川晶圓鍵合外協 2025-12-16

- 深圳高溫晶圓鍵合代工 2025-12-16

- 福建硅熔融晶圓鍵合實驗室 2025-12-16

- 安徽AR/VR電子束曝光加工平臺 2025-12-16

- 珠海陽極晶圓鍵合外協 2025-12-16

- 貴州高分辨電子束曝光技術 2025-12-16

- 西藏非標定制勻膠機有哪些 2025-12-16

- 河北映射網絡驅動器生產廠家 2025-12-16

- 合肥車位引導屏品牌 2025-12-16

- 蘇州進口整流器廠家批發價 2025-12-16

- igbt 雙脈沖測試 2025-12-16

- 單分子陣列數字ELISA使用效果 2025-12-16

- 奉賢區個性化無線控制器銷售 2025-12-16

- 江門醫療線路板雙層板 2025-12-16

- HC2303MOS售價 2025-12-16

- MTDC200晶閘管智能模塊供應商 2025-12-16