山東電阻電子元器件鍍金廠家

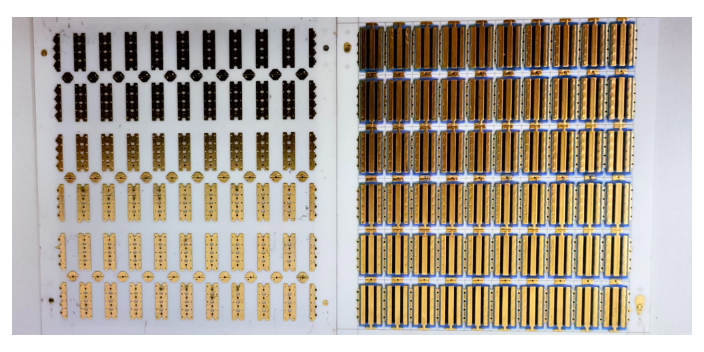

電子元器件鍍金的成本控制策略 盡管鍍金能為電子元器件帶來諸多性能優勢,但其高昂的成本也不容忽視,因此需要有效的成本控制策略。在厚度設計方面,應依據應用場景、預計插拔次數、電流要求和使用環境等因素,合理確定鍍金厚度。例如,一般工業產品中的電子接插件、印刷電路板等,對鍍金層性能要求相對較低,鍍金層厚度通常控制在 0.1 - 0.5μm,既能保證基本的導電性、耐腐蝕性和可焊性,又能有效控制成本;而在高層次電子設備與精密儀器中,由于對性能要求極高,鍍金厚度則需提升至 1.5 - 3.0μm 甚至更高。 全鍍金與選擇性鍍金的選擇也是成本控制的重要手段。出于成本考量,許多電子廠商傾向于選擇性鍍金,即在關鍵接觸面或焊接區鍍金,其他區域采用鍍鎳或其他表面處理方式。這樣既能確保關鍵部位具備金的優良特性,又能大幅削減金屬用量,降低成本。不過,選擇性鍍金對電鍍工藝的精確性要求更高,需要更精細的工藝操作來實現性能與成本的合理平衡。此外,在一些對鍍金層要求不高的應用中,還可采用閃金或超薄金處理,滿足基本的防氧化功能,進一步降低成本 。同遠表面處理公司,成立于 2012 年,專注電子元器件鍍金,技術成熟,工藝精湛。山東電阻電子元器件鍍金廠家

電子元器件鍍金工藝全解析 電子元器件鍍金工藝包含多個關鍵環節。首先是基材預處理,這是保障鍍層結合力的基礎。對于銅基元件,一般先通過超聲波清洗去除表面油污,再用稀硫酸活化,形成微觀粗糙面,以增強鍍層附著力;而陶瓷基板等絕緣基材,則需借助激光蝕刻技術制造納米級凹坑,實現金層的牢固錨定。 鍍金過程中,電流密度、鍍液溫度及成分比例等參數的精細調控至關重要。針對不同類型的元件,需采用差異化的參數設置。例如,通訊光纖模塊的鍍金件常采用脈沖電流,確保鍍層均勻性偏差控制在極小范圍內;高精密連接器則使用恒流模式,并配合穩定的電源,將電流波動控制在極低水平。鍍液溫度通常嚴格維持在特定區間,同時添加合適的有機添加劑,可細化晶粒,降低鍍層孔隙率。 完成鍍金后,還需進行后處理及檢測。后處理一般包括沖洗、干燥以及烘烤等步驟,以消除內應力,提升鍍層結合力。檢測環節涵蓋金層厚度測量、外觀檢測、附著力測試等,只有各項檢測均達標的鍍金元器件,才能進入下一生產環節 。天津基板電子元器件鍍金銠同遠表面處理公司擁有 5000 多平工廠,設備先進,高效完成電子元器件鍍金訂單。

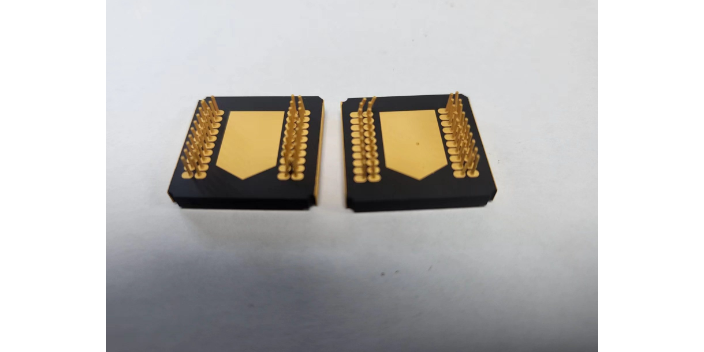

鍍金對電子元器件性能的提升體現在多個關鍵維度:導電性能:金的電阻率極低( 2.4×10??Ω?m),鍍金層可減少電流傳輸損耗,尤其在高頻信號場景(如 5G 基站元件)中,能降低信號衰減,確保數據傳輸速率穩定。同遠處理的通信元件經測試,接觸電阻可控制在 5mΩ 以內,遠優于行業平均水平。耐腐蝕性:金的化學穩定性極強,能抵御潮濕、酸堿、硫化物等腐蝕環境。例如汽車電子連接器經鍍金后,在鹽霧測試中可耐受 96 小時無銹蝕,解決了傳統鍍層在發動機艙高溫高濕環境下的氧化問題。耐磨性:鍍金層硬度雖低于某些合金,但通過工藝優化(如添加鈷、鎳元素)可提升至 800-2000HV,能承受數萬次插拔摩擦。同遠為服務器接口定制的鍍金工藝,插拔測試 5 萬次后鍍層磨損量仍小于 0.5μm。信號完整性:在精密傳感器、芯片引腳等部件中,均勻的鍍金層可減少接觸阻抗波動,避免信號反射或失真。航天級元件經其鍍金處理后,在極端溫度下信號傳輸穩定性提升 40%。焊接可靠性:鍍金層與焊料的兼容性良好,能減少虛焊、假焊風險。同遠通過控制鍍層孔隙率(≤1 個 /cm2),使電子元件的焊接合格率提升至 99.8%,降低后期維護成本。

陶瓷片的機械穩定性直接關系到其在安裝、使用及環境變化中的可靠性,而鍍金層厚度通過影響鍍層與基材的結合狀態、應力分布,對機械性能產生明顯調控作用,具體可從以下維度展開:

一、鍍層結合力:厚度影響界面穩定性陶瓷與金的熱膨脹系數差異較大(陶瓷約 1-8×10??/℃,金約 14.2×10??/℃),厚度是決定兩者結合力的關鍵。

二、抗環境沖擊能力:厚度適配場景強度在潮濕、腐蝕性環境中,厚度直接影響鍍層的抗破損能力。厚度低于 0.6 微米的鍍層,孔隙率較高(每平方厘米>5 個),環境中的水汽、鹽分易通過孔隙滲透至陶瓷表面,導致界面氧化,使鍍層的抗彎折性能下降 —— 在 180° 彎折測試中,0.5 微米鍍層的斷裂概率達 30%,而 1.0 微米鍍層斷裂概率為 5%。

三、耐磨損性能:厚度決定使用壽命在需要頻繁插拔或接觸的場景(如陶瓷連接器),鍍層厚度與耐磨損壽命呈正相關。厚度0.8 微米的鍍層,在插拔測試(5000 次,插拔力 5-10N)后,鍍層磨損量約為 0.3 微米,仍能維持基礎導電與機械結構;而厚度1.2 微米的鍍層,可承受 10000 次以上插拔,磨損后剩余厚度仍達 0.5 微米,滿足工業設備 “百萬次壽命” 的設計需求。 鍍金工藝提升元器件外觀質感,同時強化電氣性能。

電子元器件鍍金層厚度不足的重心成因解析 在電子元器件鍍金工藝中,鍍層厚度不足是影響產品性能的常見問題,可能導致導電穩定性下降、耐腐蝕性減弱等隱患。結合深圳市同遠表面處理有限公司多年工藝管控經驗,可將厚度不足的原因歸納為四大關鍵環節,為工藝優化提供方向: 1. 工藝參數設定偏差 電鍍過程中電流密度、鍍液溫度、電鍍時間是決定厚度的重心參數。若電流密度低于工藝標準,會降低離子活性,減緩結晶速度;而電鍍時間未達到預設時長,直接導致沉積量不足。2. 鍍液體系異常鍍液濃度、pH 值及純度會直接影響厚度穩定性。當金鹽濃度低于標準值(如從 8g/L 降至 5g/L),離子供給不足會導致沉積量減少;pH 值偏離比較好范圍(如酸性鍍金液 pH 從 4.0 升至 5.5)會破壞離子平衡,降低沉積效率;若鍍液中混入雜質離子(如銅、鐵離子),會與金離子競爭沉積,分流電流導致金層厚度不足。3. 前處理工藝缺陷元器件基材表面的油污、氧化層未徹底清理,會形成 “阻隔層”,導致鍍金層局部沉積困難,出現 “薄區”。4. 設備運行故障電鍍設備的穩定性直接影響厚度控制。精密電子元件鍍金,可降低接觸電阻,減少能耗。山東電阻電子元器件鍍金廠家

電子元器件鍍金能優化焊接性能,避免焊接處氧化虛接,提升電子設備組裝可靠性。山東電阻電子元器件鍍金廠家

電子元器件作為電路重心單元,其性能穩定性直接影響設備運行,而鍍金工藝憑借獨特優勢,成為高級元器件的重要表面處理方案。相較于錫、銀等鍍層,金的化學惰性極強,能為元器件構建長效防護屏障在潮濕或含腐蝕性氣體的環境中,鍍金元器件的耐氧化時長比裸金屬元器件延長10倍以上,尤其適配通信基站、醫療設備等長期運行的場景。從重心性能來看,鍍金層可大幅降低元器件接觸電阻,在高頻信號傳輸中,能將信號損耗控制在5%以內,遠優于普通鍍層的20%損耗率,這對5G芯片、衛星導航模塊等高精度元器件至關重要。同時,金的耐磨性突出,經鍍金處理的元器件引腳、連接器,插拔壽命可達10萬次以上,是裸銅元器件的50倍,有效減少設備維修頻次。工藝層面,電子元器件鍍金需精細把控細節:預處理階段通過超聲波清洗去除表面油污,再預鍍0.3-0.5微米鎳層增強結合力;鍍層厚度根據需求調整,普通接插件常用0.5-1微米,高功率元器件則需1-1.5微米;且普遍采用無氰鍍金體系,避免青化物對環境與操作人員的危害。質量檢測上,需通過X光熒光測厚儀確保厚度均勻性,借助鹽霧測試驗證耐蝕性,同時把控金層純度,確保元器件在極端溫度下仍能穩定工作,為電子設備的可靠運行筑牢基礎。山東電阻電子元器件鍍金廠家

- 貴州電容電子元器件鍍金銀 2025-12-16

- 天津金屬五金表面處理廠家 2025-12-16

- 東莞金屬五金表面處理技術 2025-12-16

- 廣東金屬五金表面處理方法 2025-12-16

- 浙江五金電子元器件鍍金供應商 2025-12-16

- 溫州金屬五金表面處理方法 2025-12-16

- 中國臺灣管殼電子元器件鍍金專業廠家 2025-12-16

- 江西管殼電子元器件鍍金供應商 2025-12-16

- 湖南厚膜電子元器件鍍金車間 2025-12-16

- 江西五金電子元器件鍍金鍍鎳線 2025-12-15

- 江門醫療線路板雙層板 2025-12-16

- 湖南有什么穩壓二極管行業 2025-12-16

- 北京atc高Q值電容 2025-12-16

- 惠山區電子元器件型號 2025-12-16

- 中國臺灣激光器參考價格 2025-12-16

- NX5032GA 40.63125MHZ晶振 2025-12-16

- 江蘇質量可控硅模塊推薦廠家 2025-12-16

- 四川交流晶閘管調壓模塊型號 2025-12-16

- 湖南氫化釜用氧氣分析儀排行榜 2025-12-16

- 怎么用鉆具量具治具工具生產設備用射頻識別盤點市價 2025-12-16